AMD zeigt ersten Wafer mit 2-Nanometer-Chips von TSMC

AMD hat einen ungewöhnlich frühen Ausblick auf seine kommende Serverprozessor-Generation gegeben. Die neue Epyc-Serie trägt den Codenamen Venice, auch bekannt als Epyc 9006.

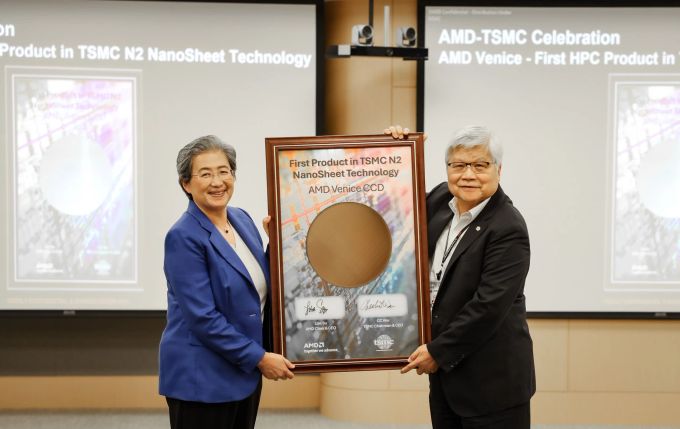

Sie wird als erstes High-Performance-Computing-Produkt (HPC) die 2-Nanometer-Technik N2 von TSMC nutzen. «Heise online» berichtet darüber.

Das grundlegende Design ist bereits abgeschlossen, und TSMC hat erste Test-Wafer mit den Compute-Chiplets gefertigt, wie AMD mitteilt.

Früher Einblick in die Zukunft der Serverprozessoren

Laut AMD ist Venice das erste 2-nm-Produkt von TSMC, das für den HPC-Bereich entwickelt wurde. TSMC definiert HPC als alles, was über Smartphone-Prozessoren hinausgeht.

Die Markteinführung ist für 2026 geplant, vermutlich im zweiten Halbjahr, wie aus den Aussagen von AMD hervorgeht.

Mit der N2-Technik vollzieht TSMC einen Technologiewechsel. Statt der bisherigen FinFETs kommen nun Gate-All-Around-Transistoren (GAAFETs) zum Einsatz, die TSMC als Nanosheets bezeichnet.

Technische Details und Gerüchte zur neuen Epyc-Generation

AMD hat bislang nur wenige Details zur neuen Generation veröffentlicht. Das Topmodell der Venice-Serie soll mit bis zu 256 Zen-6-Kernen erscheinen, verteilt auf acht Compute-Chiplets mit jeweils 32 Kernen.

Diese Chiplets werden in 2-nm-Technik gefertigt. Die Gerüchte stammen vom Youtube-Kanal «Moore's Law is Dead», dessen Trefferquote als durchwachsen gilt.

Das I/O-Die, das unter anderem die Speichercontroller und PCI-Express-Interfaces enthält, wird voraussichtlich mit älterer Fertigungstechnik produziert.

Erstes 2-nm-Compute-Chiplet für Desktop-PCs

AMD plant angeblich erstmals seit Einführung der Zen-Architektur ein separates Compute-Chiplet für Desktop-PCs.

Dieses soll 12 Zen-6-Kerne enthalten und ebenfalls bei TSMC in 2-nm-Technik gefertigt werden.

TSMC setzt auf Nanosheet-Technologie

Mit der N2-Generation setzt TSMC auf die sogenannte Nanosheet-Technologie, die eine höhere Packungsdichte und Effizienz verspricht.

Experten sehen darin einen entscheidenden Vorteil für leistungsstarke Server- und HPC-Anwendungen. AMD und TSMC haben zudem die ersten Epyc-9005-Chiplets mit 4-nm-Technik im neuen Halbleiterwerk in Arizona validiert.

Epyc-9005 werden teils in den USA gefertigt

Damit werden künftig Epyc-9005-Prozessoren teilweise in den USA gefertigt, was vor allem für US-Kunden von Bedeutung ist.

Die Compute-Chiplets für CPUs mit dem Codenamen Turin, angeführt vom 128-Kerner Epyc 9755, stammen aus dieser Produktion.

Markteinführung und Ausblick

Die Markteinführung der neuen Epyc-Prozessoren mit 2-nm-Technik ist für 2026 vorgesehen. Bis dahin werden weitere Details zu Architektur und Leistungsdaten erwartet.

Glaubst du, dass die 2-Nanometer-Technologie von AMD die Zukunft der Prozessoren beeinflussen wird?

Die Branche blickt gespannt auf die Entwicklung. Da AMD und TSMC mit der N2-Technologie neue Massstäbe im Bereich High-Performance-Computing setzen wollen.

Fazit: AMD und TSMC setzen neue Standards

Die Präsentation des ersten 2-nm-Wafers und der Ankündigung der neuen Epyc-Generation markieren AMD und TSMC einen Meilenstein in der Halbleiterentwicklung.

Die Branche erwartet mit Spannung die Markteinführung und die damit verbundenen Leistungssteigerungen, wie «Ahrefs» berichtet.